# **MOCVD GST for High Performance Phase Change Memory Devices**

J. F. Zheng<sup>1</sup>, J. Reed<sup>2</sup>, C. Schell<sup>2</sup>, W. Czubatyj<sup>2</sup>, R. Sandoval<sup>2</sup>, J. Fournier<sup>2</sup>, W. Hunks<sup>1</sup>, W. Li<sup>1</sup>, P. Chen<sup>1</sup>, C. Dennison<sup>2</sup>, S. Hudgens<sup>2</sup>, and T.Lowrey<sup>2</sup>

<sup>1</sup>ATMI Inc., 7 Commerce Drive, Danbury, CT 06810, jfzheng@atmi.com

<sup>2</sup>Ovonyx Inc., 2956 Waterview Drive, Rochester Hills, MI 48309

### **ABSTRACT**

PCM (Phase Change Memory) devices with an MOCVD GST alloy have achieved more than a 2X reduction in reset current compared to devices with PVD GST alloys. With composition and device integration optimization, PCM devices demonstrated a set speed of 12ns and a cycle endurance of 1x10<sup>9</sup>. We will discuss an MOCVD process that achieved PCM devices with a void-free fill in 70nm 3:1 aspect ratio via and process scaling up to deposit GST on 300mm wafers.

Key words: GST, MOCVD, PCM.

### 1. INTRODUCTION

Phase Change Memory (PCM) has made great progress in the past decade [1]. However, we need to follow an aggressive path of reducing reset current and increasing write speeds for application in future generation NOR memory, Storage Class Memory (SCM) and DRAM. One of the approaches is to confine the phase change memory materials, namely GST, in sub 100nm high aspect ratio device cells using a conformal deposition processes [2-4]. A CVD based process was able to fill high aspect ratio dash structures of 7.5nm width to achieve 160uA reset current and 50ns set speed [3]. An ALD process has filled high aspect ratio hole structure of less than 100nm as well [5]. In this paper, we first focus on material properties of the MOCVD alloy. We achieved a 2-3X reset current reduction using our optimized MOCVD alloy in devices compared to using PVD GST alloys. We demonstrated faster than 20ns set speed operation in the MOCVD alloy based device. Then we will present void-free fill of MOCVD GST in 3:1 aspect ratio holes for high performance device operation in sub 70nm diameter devices and the scaling of such process to a 300mm GST deposition system.

# 2. EXPERIMENTS

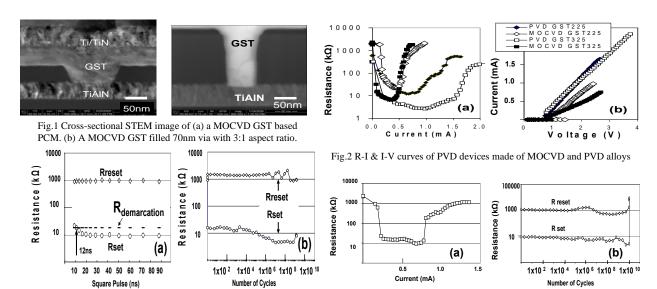

We deposited MOCVD films to evaluate MOCVD GST alloys for device application in a coupon sized deposition tool [3]. Fig.1 shows two types of device structures used in our study. Fig. 1a is a shallow pore test structure for evaluating MOCVD alloy properties in device applications, in which PVD GST alloy deposition can also be used to make devices for comparison. Fig.1b is a 3:1 high aspect ratio deep pore structure which we filled with a void-free MOCVD alloy. The test structures have nominal design dimensions ranging from 70nm to 200nm. The detailed description of the structures and processes can be found in [4, 6].

# 3. RESULTS & DISCUSSION

Fig. 2 shows the comparison of R-I curve (2a) and I-V curves (2b) of PCM devices using MOCVD GST 225 and GST 325 alloys and the corresponding PVD GST 225 and 325 alloys for comparison in structures similar to Fig.1a. Devices using MOCVD GST 225 and 325 alloys show more than a 2X and 3X reduction of reset current when compared with devices using PVD GST 225 and 325 alloys. Devices made from a MOCVD GST 325 alloy showed the best electrical performance [6].

Fig. 3 shows fast speed performance of a PCM device with structures similar to Fig.1a and with an optimized alloy composition and device integration. Set speed as fast as 12ns was measured and shown in Fig.3a. Such devices also demonstrated cycle life to 1x10<sup>9</sup> cycles without failure, as shown in Fig.3b. The devices tested had a CD range of 88~106nm as measured by SEM and all showed similar set speed. Since the fast set speed characteristics does not depend on device dimension or GST alloy volume in the device, we conclude it is due to the characteristics of the MOCVD alloy.

Fig. 3 PCM device with MOCVD GST at optimal alloy composition and process shows set speed of 12ns. It also cycles more than 1x10°.

Fig. 4 PCM device with 3:1 aspect ratio and 70nm, similar to that of Fig.1b. shows  $\sim 1 \times 10^{10}$  cycles and Rreset/Rset ratio of about 100

Fig. 4 shows the I-R curve (Fig. 4a) and cycling characteristics (Fig. 4b) of a PCM device made with MOCVD GST filling a 70nm 3:1 aspect ratio via [4], in the structure as shown in Fig.1b. Devices cycled more than 1x10<sup>10</sup> times. We will discuss development efforts to duplicate PCM device results from the coupon process in a 300mm wafer system.

### 4. CONCLUSION

PCM devices made from an MOCVD alloy demonstrated 2-3X less reset current compared with that from a PVD alloy in 100nm shallow pore devices. PCM devices in same test structures with optimized composition and integration achieved a 12ns set speed and cycle endurance of  $1x10^9$ . We show for the first time that such high device performance is mostly determined by the alloy instead of the use of advanced device structures. We also showed that we can fill an MOCVD GST alloy void-free in 3:1 aspect ratio 70nm advanced via structure and demonstrated cycle endurance better that  $1x10^{10}$ .

## REFERENCES

- 1. R. Bez, "Chalcogenide PCM: A memory technology for next decade", IEDM Tech. Dig., 2009, p.89

- 2. J. I. Lee, *et al*, "Highly Scalable Phase Change Memory with CVD GeSbTe for sub 50nm generation," Symp. VLST Tech dig. 2007, p. 102

- 3. D. H. Im, *et al*, "A unified 7.5nm dash-type confined cell for high performance PRAM device", IEDM Tech. Dig., 2008, p.211

- 4. J. F. Zheng, *et al*, "Conformal MOCVD Deposition of GeSbTe in High Aspect Ratio Via Structures for Phase Change Memory Applications", Proceedings of MRS Spring Meeting, 2009, p.1160

- 5. M. Ritala, et al, "Atomic Layer Deposition of Germanium Antimony Telluride Thin Films", E\PCOS 2009, p.151.

- 6. J. F. Zheng, et al, "MOCVD Ge<sub>3</sub>Sb<sub>2</sub>Te<sub>5</sub> for PCM Applications", to be published in IEEE Electron Device Lett.

## **Biography**

Jun-Fei Zheng received Ph.D. degree in Materials Science from University of California at Berkeley in 1994. From 1994 to 2007, he worked at Intel Corporation in Frontend process and advanced device integration. In 2007, he joined ATMI as Advisory Technologist. He is currently MOCVD GST project technical leader. He holds 22 U.S. patents and has more than 30 publications in the areas of semiconductor materials, transistors, memory devices, and optoelectronic devices.